RANWALK: Random walks for integrated circuit design

Duration: 30 months starting in Spring 2022

Framework: Research-Innovate-Create (Greek Ministry of Development)

Partners: HELIC / ANSYS Hellas (coord.), U Patras, Athena RC.

Abstract

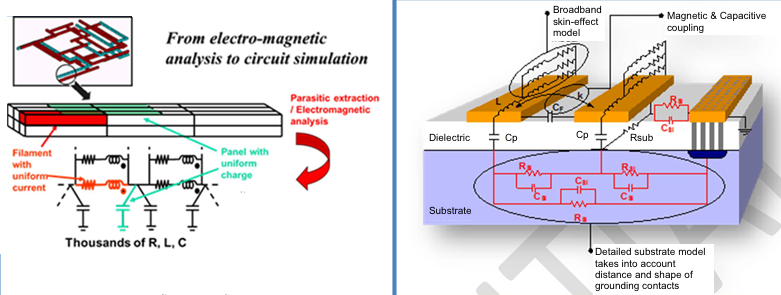

The choice of high operating frequencies is today the biggest challenge in micro-electronics, as the need to design and implement corresponding circuit devices for transceivers in critical applications is imperative. In the project, the circuits to be designed will have two characteristics: they are devices with wide application in transceiver systems, and their passive elements play a decisive role in performance. In addition, the operation in hifh frequencies will highlight the capabilities of the improved method for extracting parasitic capacities. A key element of this modeling method and the overall approach of the project is the method of random walks between sets of conductors, which is based on solving the Laplace equation and determining the Green function in cubic regions. We aim at the geometric modeling of the physical design of the conductors, as well as the efficient and robust calculation of the above electrostatic parameters, with the ultimate goal of a fast simulation of the accuracy of the circuit. We focus on calculating the Maximum Empty Cube between rectangular conductors, and develop large-scale geometric software.